# **Electronics Engineering**

## **Digital Circuits**

Comprehensive Theory with Solved Examples and Practice Questions

#### **MADE EASY Publications**

Corporate Office: 44-A/4, Kalu Sarai (Near Hauz Khas Metro Station), New Delhi-110016

E-mail: infomep@madeeasy.in

Contact: 011-45124612, 0-9958995830, 8860378007

Visit us at: www.madeeasypublications.org

#### **Digital Circuits**

© Copyright, by MADE EASY Publications.

All rights are reserved. No part of this publication may be reproduced, stored in or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photo-copying, recording or otherwise), without the prior written permission of the above mentioned publisher of this book.

First Edition: 2015 Second Edition: 2016 Third Edition: 2017 Fourth Edition: 2018 Fifth Edition: 2019 **Sixth Edition: 2020**

## **Contents**

## **Digital Circuits**

| Ch  | Chapter 1                                          |         |            | Chapter 5                                    |     |  |  |

|-----|----------------------------------------------------|---------|------------|----------------------------------------------|-----|--|--|

| Νι  | ımber Systems                                      | 1       | Co         | unters                                       | 152 |  |  |

| 1.1 | Digital Number Systems (Positional Weight Sys      | tem) 2  | 5.1        | Asynchronous Counters (or Ripple Counters)   | 154 |  |  |

| 1.2 | Codes                                              | 7       | 5.2        | Decoding Errors (Glitches or Spikes)         | 157 |  |  |

| 1.3 | Arithmetic Operations                              | 11      | 5.3        | Synchronous Counters                         | 160 |  |  |

| 1.4 | Signed Number Representation                       | 15      | 5.4        | Design of Synchronous Counters               | 171 |  |  |

| 1.5 | Over Flow Concept                                  | 19      | 5.5        | Pulse Train Generation (Sequence Generators) | 182 |  |  |

|     | Student's Assignments                              | 20      |            | Student's Assignments                        | 192 |  |  |

| Cł  | napter 2                                           |         | Ch         | napter 6                                     |     |  |  |

|     | olean Algebra and Logic Gates                      | 21      | Sy         | nthesis of Synchronous                       |     |  |  |

| 2.1 | Logic Operations                                   |         | Se         | quential Circuits                            | 194 |  |  |

| 2.2 | Laws of Boolean Algebra                            |         | 6.1        | Finite State Machine (FSM)                   | 194 |  |  |

| 2.3 | Boolean Algebric Theorems                          |         | 6.2        |                                              |     |  |  |

| 2.4 | Minimization of Boolean Functions                  |         | 0.2        | or Finite State Machine                      | 204 |  |  |

| 2.5 | Representation of Boolean Functions                | 27      |            | Student's Assignments                        |     |  |  |

| 2.6 | Karnaugh Map                                       | 32      |            | Stadent 371331gmment3                        | 220 |  |  |

| 2.7 | Logic Gates                                        | 42      | Ck         | napter 7                                     |     |  |  |

|     | Student's Assignments                              | 63      |            |                                              |     |  |  |

|     |                                                    |         | Pro        | ogrammable Logic Devices and                 |     |  |  |

| Ch  | napter 3                                           |         | Me         | emories                                      | 229 |  |  |

| Co  | mbinational Circuits                               | 65      | 7.1        | Programmable Logic Devices                   | 230 |  |  |

| 3.1 | Design Procedure for Combinational Circuit         | 65      | 7.2        | Semiconductor Memories                       | 243 |  |  |

| 3.2 | Adders and Subtractors                             | 73      |            | Student Assignments                          | 248 |  |  |

| 3.3 | Binary Adders                                      | 78      |            | 3                                            |     |  |  |

| 3.4 | Code Converters                                    | 89      | Ch         | napter 8                                     |     |  |  |

| 3.5 | Parity Bit Generators and Checkers                 | 91      |            |                                              |     |  |  |

| 3.6 | Magnitude Comparators                              | 93      | Lo         | gic Families                                 | 249 |  |  |

| 3.7 | Encoders                                           | 95      | 8.1        | Switching Circuits                           | 250 |  |  |

| 3.8 | Decoders                                           | 98      | 8.2        | Classification of Digital Logic Family       | 254 |  |  |

| 3.9 | Multiplexers                                       | 105     | 8.3        | Characteristics of Digital Logic Family      | 255 |  |  |

|     | Demultiplexers                                     |         | 8.4        | Logic Families                               |     |  |  |

| 3.1 | Hazards and Hazard-free Realization                | 114     |            | Student's Assignments                        |     |  |  |

|     | Student's Assignments                              | 122     |            | Statent's /1331g/michts                      | 273 |  |  |

| Cŀ  | napter 4                                           |         | Ch         | napter 9                                     |     |  |  |

| Fli | p-Flops and Registers                              | 125     | <b>A</b> / | D and D/A Converters                         | 298 |  |  |

| 4.1 | Latches and Flip-Flops                             |         | 9.1        | Digital to Analog Converter                  | 298 |  |  |

| 4.2 | Conversion from One Type of Flip-Flop to Another T | Type136 | 9.2        | Analog to Digital Converters                 | 312 |  |  |

| 4.3 | Operating Characteristics of a Flip-Flop           | 139     |            | Student's Assignments                        | 322 |  |  |

| 4.4 | Application of Latches and Flip-Flops              | 142     |            |                                              |     |  |  |

| 4.5 | Registers                                          | 143     |            |                                              |     |  |  |

CHAPTER 6

## Synthesis of Synchronous Sequential Circuits

#### Introduction

#### State Diagram (State graph)

It is a pictorial representation of the relationships between the present state, the input, the next state and the output of a sequential circuit, i.e. the state diagram is a pictorial representation of the behaviour of a sequential circuit.

#### State table

The state table is a tabular representation of the state diagram. Even though the behaviour of a sequential circuit can be conveniently described using a state diagram, for its implementation the information of the state diagram is to be translated into a state table. Both the state diagram and the state table contain the same information.

#### **6.1 Finite State Machine (FSM)**

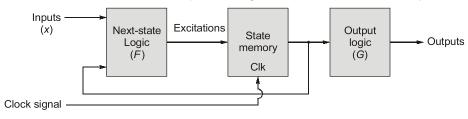

- Finite state machines are sequential circuits whose past histories can affect their future behaviour in only a finite number of ways, i.e. they are machines with a fixed number of states.

- A sequential circuit is referred to as a finite state machine (FSM).

- Finite state machines are of two types. They differ in the way the output is generated. They are

- 1. Mealy type model 2. Moore type model

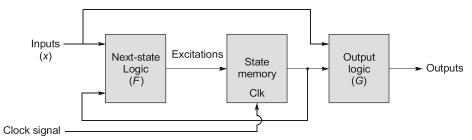

#### 6.1.1 Mealy Machine

In this model, the output depends on both the present state of the circuit and the present inputs.

NS = F(PS, X)

Output = G(PS, X)

F and G are some logic functions.

PS = Present state

NS = Next state

X =Present inputs

Input changes may affect the output of the logic circuit.

It requires less number of states for implementing a function than that of Moore model.

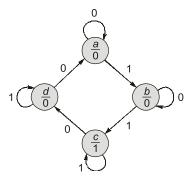

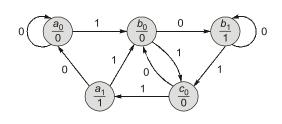

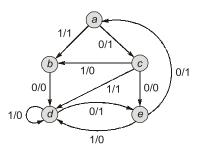

State diagram and state table for a Mealy circuit are given below.

| DC | NS output |       |  |  |

|----|-----------|-------|--|--|

| PS | X = 0     | X = 1 |  |  |

| а  | a, 0      | b, 1  |  |  |

| b  | b, 1      | c, 0  |  |  |

| С  | d, 0      | c, 1  |  |  |

| d  | d, 0      | a, 1  |  |  |

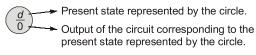

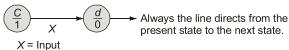

State diagram

Stable table

X =Input and Y =Output

In the Mealy model, the output depends on the present input. Hence both input, output are represented on the directed lines.

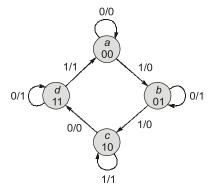

#### 6.1.2 **Moore Machine**

In this model, the output depends only on the present state of the circuit.

$$NS = F(PS, X)$$

Output =  $G(PS)$

F and G are some logic functions.

PS = Present state

NS = Next state

X =Present inputs

Input changes do not affect the output of the logic circuit.

It requires more number of states for implementing a function than that of Mealy model.

www.madeeasypublications.org

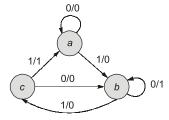

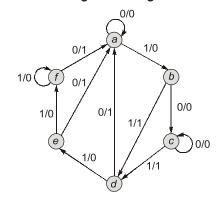

State diagram and state table for a Moore circuit are given below.

| PS | NS Input |       | Present |

|----|----------|-------|---------|

| P5 | X = 0    | X = 1 | output  |

| а  | а        | b     | 0       |

| b  | b        | С     | 0       |

| С  | d        | С     | 1       |

| d  | а        | d     | 0       |

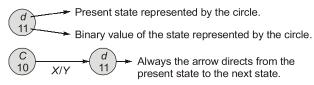

State diagram

State table

In the Moore model, the output depends only on the present state of the circuit and it is independent of the input applied. Hence, the present output is represented inside the circle belongs to the present state and input is represented on the directed line.

#### Example - 6.1

Draw the equivalent Moore state diagram for the following Mealy state diagram.

#### **Solution:**

In a Moore state diagram, each state is associated with a fixed output.

States for the Moore state diagram, corresponding to the given Mealy state diagram, can be assigned as shown below.

| Mealy State      | Equivalent Moore State |

|------------------|------------------------|

| a, with output 0 | a <sub>0</sub>         |

| a, with output 1 | a <sub>1</sub>         |

| b, with output 0 | $b_0$                  |

| b, with output 1 | <i>b</i> <sub>1</sub>  |

| c, with output 0 | $c_0$                  |

In the given Mealy state diagram, there no transition that produces next state as "c" with output "1". Hence, there is no need a state equivalent to "c" with output "1", i.e.  $c_1$  in Moore model.

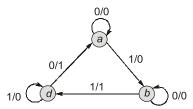

The state table and state diagram of the required Moore model can be given as,

| Present state         | Next state (output)       |                           |  |  |

|-----------------------|---------------------------|---------------------------|--|--|

| rieselli state        | X = 0                     | X = 1                     |  |  |

| a <sub>0</sub>        | a <sub>0</sub> (0)        | <i>b</i> <sub>0</sub> (0) |  |  |

| a <sub>1</sub>        | a <sub>0</sub> (0)        | <i>b</i> <sub>0</sub> (0) |  |  |

| $b_0$                 | <i>b</i> <sub>1</sub> (1) | c <sub>0</sub> (0)        |  |  |

| <i>b</i> <sub>1</sub> | <i>b</i> <sub>1</sub> (1) | c <sub>0</sub> (0)        |  |  |

| $c_0$                 | <i>b</i> <sub>0</sub> (0) | a <sub>1</sub> (1)        |  |  |

State table

State diagram

#### Example - 6.2

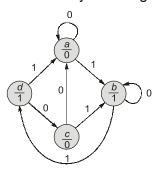

Draw the equivalent Mealy state diagram for the following Moore state diagram.

#### **Solution:**

Same state notations can be followed in the corresponding Mealy state diagram of the given Moore state diagram.

The state table and state diagram of the required Mealy model can be given as,

| Present state | Next  | state | Output |       |  |

|---------------|-------|-------|--------|-------|--|

| Fresent state | X = 0 | X = 1 | X = 0  | X = 1 |  |

| а             | а     | ь     | 0      | 1     |  |

| b             | b     | d     | 1      | 1     |  |

| С             | а     | b     | 0      | 1     |  |

| d             | С     | а     | 0      | 0     |  |

State table

State diagram

#### **State Reduction**

- The state reduction technique basically avoids the introduction of redundant states.

- The reduction in redundant states reduces the number of flip-flops and logic gates, reducing the cost of the final circuit.

- Two states are said to be equivalent if every possible set of inputs generate exactly the same output and the same next state.

- When two state are equivalent, one of them can be removed without altering the input-output relationship.

- Let us illustrate the reduction technique with an example.

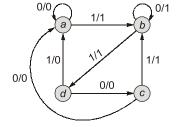

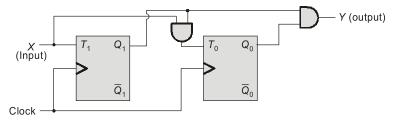

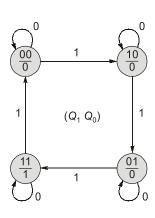

Example - 6.3 Develop a state diagram for the logic circuit shown in the figure below.

#### **Solution:**

Excitations of the flip flops are,  $T_1 = X$  and  $T_0 = Q_1 X$ Output signal,  $Y = Q_1 Q_0 \Rightarrow$  Moore circuit

The state table and state diagram of the given sequential circuit can be developed as shown below.

| Present state  |       | Input | Excit                 | ations | Next                        | tstate  | Output |

|----------------|-------|-------|-----------------------|--------|-----------------------------|---------|--------|

| Q <sub>1</sub> | $Q_0$ | X     | <i>T</i> <sub>1</sub> | $T_0$  | Q <sub>1</sub> <sup>+</sup> | $Q_0^+$ | Υ      |

| 0              | 0     | 0     | 0                     | 0      | 0                           | 0       | 0      |

| 0              | 0     | 1     | 1                     | 0      | 1                           | 0       | 0      |

| 0              | 1     | 0     | 0                     | 0      | 0                           | 1       | 0      |

| 0              | 1     | 1     | 1                     | 0      | 1                           | 1       | 1      |

| 1              | 0     | 0     | 0                     | 0      | 1                           | 0       | 0      |

| 1              | 0     | 1     | 1                     | 1      | 0                           | 1       | 0      |

| 1              | 1     | 0     | 0                     | 0      | 1                           | 1       | 1      |

| 1              | 1     | 1     | 1                     | 1      | 0                           | 0       | 0      |

#### Example - 6.4

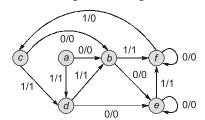

#### Reduce the following state diagram:

#### **Solution:**

• The state table of the given state diagram is,

|    | _NS_  |       | Out   | tput  |

|----|-------|-------|-------|-------|

| PS | X = 0 | X = 1 | X = 0 | X = 1 |

| а  | b     | d     | 0     | 1     |

| b  | е     | f     | 0     | 1     |

| С  | b     | d     | 0     | 1     |

| d  | е     | b     | 0     | 1     |

| е  | е     | f     | 0     | 1     |

| f  | f     | С     | 0     | 0     |

"b" and "e" are said to be equivalent states. So, remove "e" and replace it with "b".

"a" and "c" are said to be equivalent states. So, remove "c" and replace it with "a".

So, the reduced state table is,

|  | PS $X = 0$ $X = 1$ |   | Out   | tput  |   |

|--|--------------------|---|-------|-------|---|

|  |                    |   | X = 0 | X = 1 |   |

|  | а                  | b | d     | 0     | 1 |

|  | b                  | b | f     | 0     | 1 |

|  | d                  | b | b     | 0     | 1 |

|  | f                  | f | а     | 0     | 0 |

No further equivalent states are found. So, it is not possible to reduce further.

Now, the reduced state diagram can be drawn from the reduced state table as shown below:

#### Example - 6.5

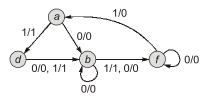

#### Reduce the following state diagram:

#### **Solution:**

The state table of the given state diagram is,

|    | N     | S     | Out   | put   |

|----|-------|-------|-------|-------|

| PS | X = 0 | X = 1 | X = 0 | X = 1 |

| а  | С     | b     | 1     | 1     |

| b  | d     | С     | 0     | 0     |

| С  | g     | d     | 0     | 1     |

| d  | е     | f     | 1     | 0     |

| е  | а     | f     | 1     | 0     |

| f  | g     | f     | 1     | 0     |

| g  | а     | f     | 1     | 0     |

"g" and "e" are said to be equivalent states. So, remove "g" and replace it with "e".

The reduced state table is,

| PS  | NS<br>X = 0 X = 1 |       |       | tput  |

|-----|-------------------|-------|-------|-------|

| . • | X = 0             | X = 1 | X = 0 | X = 1 |

| а   | С                 | b     | 1     | 1     |

| b   | d                 | С     | 0     | 0     |

| С   | е                 | d     | 0     | 1     |

| d   | е                 | f     | 1     | 0     |

| е   | а                 | f     | 1     | 0     |

| f   | е                 | f     | 1     | 0     |

Postal Study Package 2021

"e" and "f" are said to be equivalent states. So, remove "f" and replace it with "e".

The reduced state table is,

| PS | X = 0  X = 1 |   | Out<br>X = 0 |   |

|----|--------------|---|--------------|---|

| а  | С            | b | 1            | 1 |

| b  | d            | С | 0            | 0 |

| С  | е            | d | 0            | 1 |

| d  | е            | d | 1            | 0 |

| е  | а            | d | 1            | 0 |

No further reduction is possible, hence the reduced state diagram is as shown below:

#### Example - 6.6

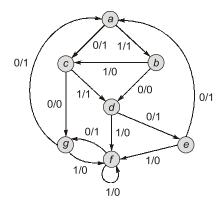

Reduce the following state diagram:

#### **Solution:**

The state table of the state diagram can be given as follows:

| Present | Next State |       | Output |       |     |

|---------|------------|-------|--------|-------|-----|

| State   | X=0        | X = 1 | X=0    | X = 1 |     |

| а       | а          | b     | 0      | 0     | X = |

| [ b     | С          | d     | 0      | 1]    |     |

| [ c     | С          | d     | 0      | 1     |     |

| d       | а          | е     | 1      | 0     |     |

| е       | а          | f     | 1      | 0     |     |

| f       | а          | f     | 1      | 0     |     |

= Input

States "b" and "c" have same next state and output for a given value of input. So, these two states are said to be equal and we can replace the state "c" with state "b".

States "e" and "f" have same next state and output for a given value of input. So, these two states are said to be equal and we can replace the state "f" with state "e".

After replacing states "c" and "f" with states "b" and "e" respectively, the resultant state table is as follows:

| Present | Next State |       | Output |       |

|---------|------------|-------|--------|-------|

| State   | X = 0      | X = 1 | X=0    | X = 1 |

| а       | а          | b     | 0      | 0     |

| b       | b          | d     | 0      | 1     |

| d       | а          | е     | 1      | 0     |

| е       | а          | е     | 1      | 0     |

States "d" and "e" have same next state and output for a given value of input. So, these two states are said to be equal and we can replace the state "e" with state "d".

After replacing state "e" with state "d", the resultant state table is as follows:

| Present | Next State |       | Output |       |

|---------|------------|-------|--------|-------|

| State   | X = 0      | X = 1 | X=0    | X = 1 |

| а       | а          | b     | 0      | 0     |

| b       | b          | d     | 0      | 1     |

| d       | а          | d     | 1      | 0     |

- In the above state table, no two states have same next state and output for a given value of input. Hence there are no equal states and it is not possible to reduce the state table further.

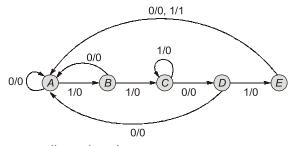

- From the above table, the reduced state diagram of the given state diagram can be drawn as follows:

Example - 6.13 Develop Mealy and Moore type of state diagrams for a one input-one output sequence detector, to detect the sequence "110011".

#### **Solution:**

#### For Mealy model design

For Mealy model, the number of unique states = number of bits in the sequence to be detected. In this question, the sequence to be detected is "11011".

Number of bits in the sequence = 5 ⇒ Number of unique states = 5 (let us say A, B, C, D, E)

#### If overlapping sequences are not allowed to detect:

$$A: X \Rightarrow \begin{cases} \text{if } X = 0 \Rightarrow \text{Remains in the state } A \\ \text{if } X = 1 \Rightarrow \text{Moves to the state } B \end{cases}$$

in both cases  $o/p = 0$

$$B: 1 X \qquad \Rightarrow \begin{array}{l} \text{if } X = 0 \Rightarrow \text{Moves to the state } A \\ \text{if } X = 1 \Rightarrow \text{Moves to the state } C \end{array} \right\} \text{ in both cases o/p} = 0$$

$$C: 1 \ 1 \ X \implies \begin{cases} \text{if } X = 0 \Rightarrow 110 \Rightarrow \text{Moves to the state } D \\ \text{if } X = 1 \Rightarrow 111 \Rightarrow \text{Remains in the state } C \end{cases}$$

in both cases o/p = 0

E: 1 1 0 1 X

$$\Rightarrow$$

if  $X = 0 \Rightarrow 11010 \Rightarrow$  Moves to the state  $A \Rightarrow o/p = 0$  if  $X = 1 \Rightarrow 11011 \Rightarrow$  Moves to the state  $A \Rightarrow o/p = 1$

As overlapping is not permitted, after the detection of the desired sequence, the machine moves to the first state.

The resulting state diagram is,

#### If overlapping sequences are allowed to detect:

For the overlapping case, the state transitions from the states A, B, C, D are same as that of the nonoverlapping case. Only the state transitions from the state E will change as follows,

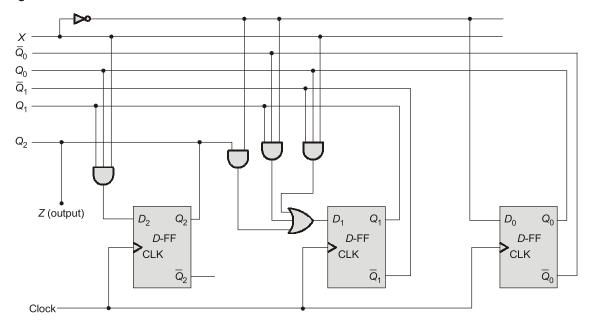

#### Logic circuit:

#### Student's **Assignments**

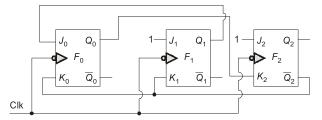

#### Q.1 Consider the counter circuit shown in the figure below:

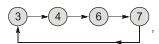

The counter is designed such that it counts the states

then which of the following statements about this counter is true?

- (a) The counter enters into a lockout state if the counter starts from (5)<sub>10</sub>

- (b) The counter enters into a lockout state if the counter starts from (2)<sub>10</sub>

- (c) The counter enters into a lockout state if the counter starts from (3)<sub>10</sub>

- (d) The counter do not enters into a lockout state.

- (a)  $\overline{A}\overline{B} + AQ$

- (b)  $\overline{A}\overline{B} + \overline{B}Q$

- (c) Both A and B

- (d) None of above

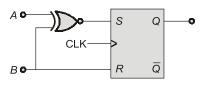

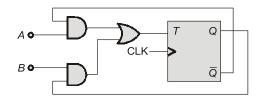

- Q.7 What is represented by digital circuit given below?

- (a) An S-R flip-flop with A = S and B = R

- (b) A J-K flip-flop with A = K and B = J

- (c) A J-K flip-flop with A = J and B = K

- (d) An S-R flip-flop with A = R and B = S

- ANSWERS

- **1**. (d) **2**. (c)

- **3**. (d)

- **4**. (a)

- **5**. (c)

- **6**. (c)

- 7. (c & a)

## Student's Assignments

2

Q.1 Design a 4-bit serial-in, serial-out, bidirectional shift register using D-flip flops. The design should consist a mode control bit 'M'. When M=0, the register should work as shift-left shift register and when M=1, the register should work as shift-right shift register.